반도체 공정 [18] 박막공정 (4) ALD(Atomic Layer Deposition)

반도체 공정 [16] 박막공정 (2) PVD(Physical Vapor Deposition): Evaporation, Sputtering2025.02.12 - [반도체 공부/반도체 공정] - 반도체 공정 [15] 박막공정 (1) 박막 개요 반도체 공정 [15] 박막공정 (1) 박막 개요2025.

mayunchem.tistory.com

반도체 칩은 설계한 의도대로 각 소자들을 구동하여 원하는 기능(function)을 수행하는 역할을 한다.

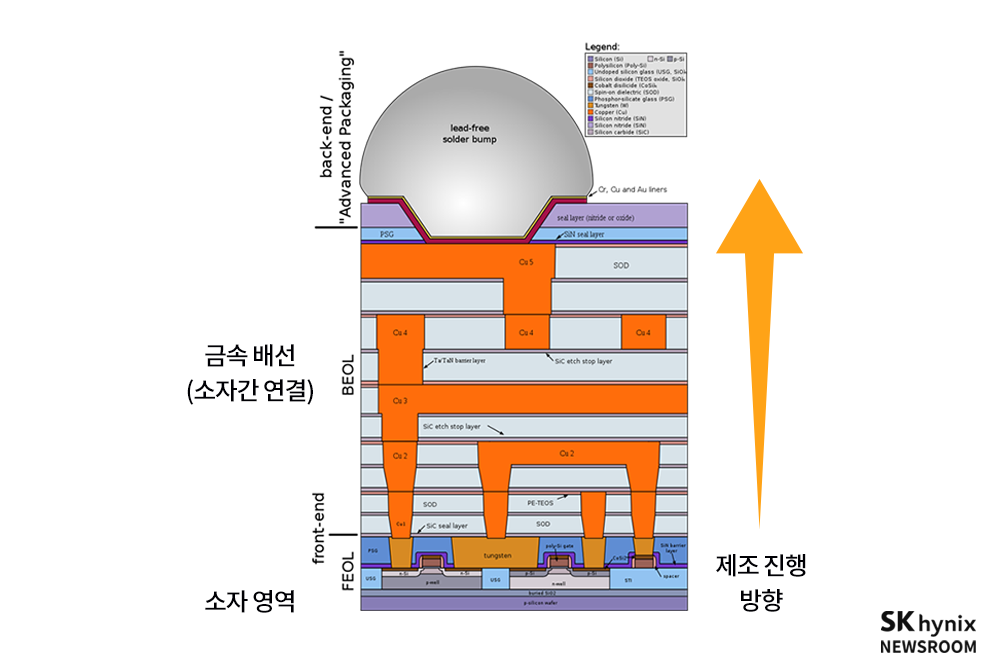

금속 배선 공정

금속 배선 공정은 웨이퍼 위에 올라간 수많은 반도체 회로들이 동작하기 위해 외부에서 받은 전기적 신호가 잘 전달되도록, 반도체 회로 패턴에 전기길을 까는 과정이다.

반도체 소자들은 개별적인 상태로 아무런 역할을 하지 못한다. 전자 기판 위 개별 소자들이 납땜 없이 작동하지 못하듯, 웨이퍼 위의 트랜지스터들도 서로 연결 되고 외부전원을 받고, 처리가 끝난 데이터를 다음 영역으로 옮겨주어야 작동을 할 수 있다.

동일한 소자도 연결형태에 따라 CPU, GPU 등 다양한 형태의 반도체가 되기 때문에 금속 배선 공정은 반도체에 '목적'을 부여하는 공정이다.

반도체 회사들은 금속 배선을 만들기 위해 포토, 식각 등의 공정을 거치지만, 이전과는 달리 금속이 많이 쓰인다는 특징이 있다.

금속 도선이 제 역할을 하기 위해서는 아래와 같은 조건을 가지고 있어야 한다.

금속 재료의 필요 조건

1. 웨이퍼와의 부착성

- Si 웨이퍼 위 얇은 박막으로 증착할 수 있도록 부착이 쉬워야 하며, 부착 강도도 우수해야한다.

2. 전기 저항이 낮은 물질

- 전류 전달을 하기 때문에 전기 저항이 낮아야 한다. 저항이 높은 경우 신호의 지연이 발생하고, 전력의 손실이 발생할 수 있다.

3. 열 화학적 안정성

- 금속 배선의 후속 과정에서 금속선의 특성이 변하거나, 파괴되면 안된다.

4. 패턴 형성의 용이성

- 회로 패턴에 따라 금속 선을 형성할 수 있어야 한다. 포토, 에치 공정등을 통해 패턴의 구현이 가능해야 한다.

5. 높은 신뢰성

- 반도체의 미세화 트랜드에 맞게, 적은 단면으로 제작 시 끊김이 있어서는 안된다.

6. 제조 가격

- 제조 가격이 높으면 대량 생산이 어려우므로 합리적인 가격이어야 한다.

7. 장기적인 신뢰성

- 10년 정도 기능이 동작할 수 있는 신뢰성이 필요하다.

보통 이런 금속 배선 재료로는 Al(알루미늄)과 Cu(구리)가 대표적으로 사용되며, 그 외에는 티타늄이나 텅스텐이 있다.

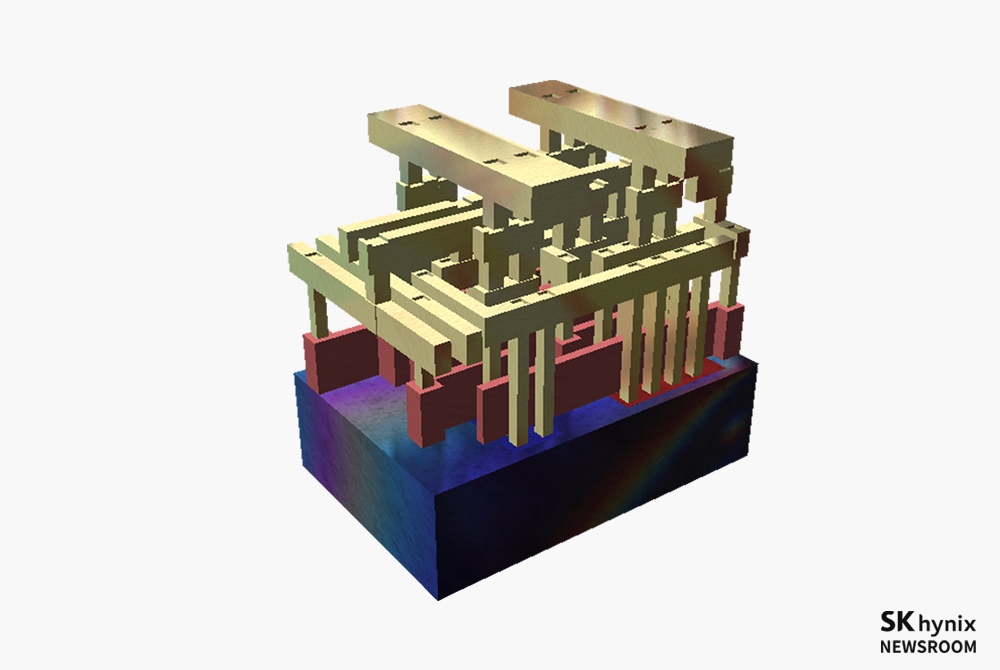

이러한 조건을 만족하는 금속 물질로 절연체에 패턴을 만들어 그 패턴 속에 채워 넣는 배선 공정을 진행하며, 보통 패턴 형성 -> 금속 증착 및 도금 -> CMP 연마 로 도전 영역과 절연영역을 분리하는 과정을 반복해서 진행해 3차원의 배선을 완성할 수 있다.

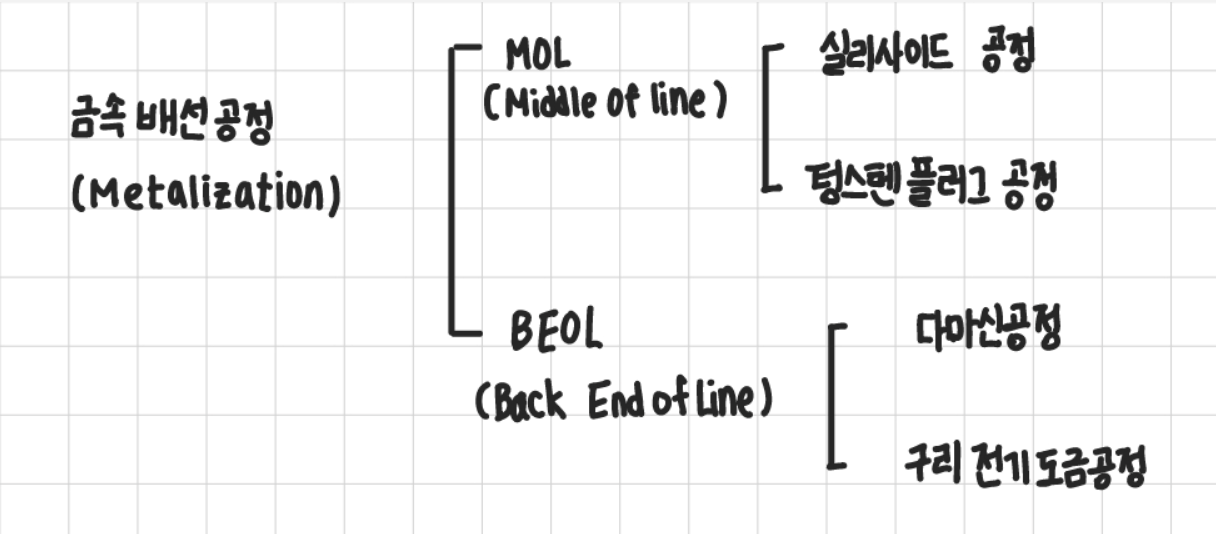

금속 배선 공정의 단계

금속 배선 공정의 단계를 간단히 정리해 보았다.

1) 실리사이드(Silicide) 공정

실리사이드는 실리콘과 금속이 반응하여 형성된 화합물이다.

반도체 공정에서 실리콘이 금속과 반응하는 경우는, MOSFET에서는 1) 소스와 드레인의 실리콘에 단자를 형성하는 경우와 2) gate 전극이 Poly-Si 일 때 빠른 신소 전달을 위해 Poly-Si의 상부를 금속과 반응시킬 때가 있다.

1)번 공정을 실리 사이드 공정, 2)번 공정을 폴리사이드라고 한다. 이러한 공정을 하는 이유는 금속과 실리콘을 반응시켜 저항이 낮은 상태의 물질을 형성하기 위해서이다. 최첨단 공정에서는 2) 폴리사이드(Polyside) 는 잘 사용하지 않고 있다(이전세대에서 사용되었다).

가장 흔히 사용되는 실리사이드 물질에는 TiSi2, NiSi, CoSi2 등이 Ohmic Contact으로 사용되고 있고. WSi2는 레지스터의 저항 물질로 사용되고 있다.

반도체 공정에서는 기판이 실리콘이기 때문에 금속을 증착한 후 고온 열처리를 하면 실리사이드를 만들 수 있다. Source와 Drain의 ohmic contact을 위해서는 metal-semiconductor 접합을 형성해야 하는데, 실리콘이 드러난 상태에서 금속의 증착과 열처리 만으로도 쉽게 만들수 있어 대부분의 Contact 공정에서 사용되고 있다.

이러한, 실리사이드 물질의 필수 조건은 낮은 저항, 열적 안정성, 물질적 안정성 들이 있다. 또한, 영역을 분리하지 않고 사용하기 때문에 동일한 물질의 실리사이드로 N형과 P형 실리콘에 모두 낮은 컨택트 저항 특성을 물질을 사용해야 한다.

추가로 이전 50nm 공정에서는 CoSi2가 많이 사용되었으나, 선폭이 짧아지며 물질이 뭉치는 Agglomeration 현상이 나타났고, 회로가 단선되는 현상까지 발생하며, NiSi2가 사용되기 시작하였다. 20nm까지는 활발히 사용되었으나, P 타입의 MOSFET의 저항이 높고 열처리를 하면 Ni의 확산이 과도해지면서 실리사이드와 실리콘간 계면이 불안해지며 Implantation 현상으로 손실전류가 발생하는 현상으로 TiSi2가 현재는 사용되고 있다.

공정을 순서대로 살펴보자.

1. 산화물 절연막을 증착한 후, Contact가 만들어질 공간에 패턴을 형성한다. 이후 에치 공정으로 트랜치를 만들어준다.

2. 금속-반도체 접합을 위해 Ti를 PVD 방법으로 증착한다. (또는 Sputtering Etch 공정 후 in-situ로 Ti를 증착시킨다.) Source/ Drain 단자는 도핑 농도가 높아야 한다.

3. 전극물의 산화 방지를 위해 in-situ 공정으로 TiN을 CVD 방법으로 증착시킨다. 이는, Ti의 산화를 방지하고 W(Tungsten)을 증착할 때 원자핵의 생성이 일어날 자리이자, 불소 부산물의 확산의 방지목적으로 증착한다.

4. 800도 수준에서 레이저를 이용해 어닐링 공정을 진행한다. 이때 Ti와 기판의 실리콘이 반응하며 TiSi2가 만들어지며 ohmic contact가 형성된다.

5. BEOL 공정의 배선과 연결될 수 있도록 플러그를 만들어준다. CVD 방식으로 W을 트랜치 내부에 채워서 배선을 연결하며, 이때 텅스텐은 내부뿐 아니라 산화물 절연막의 위까지 웨이퍼 전부를 뒤덮어 void가 생기지 않도록 성장시킨다. 이때 void가 생긴다면 Seam 결함이 발생해 BEOL 공정에서의 구리의 비정상적 확산이 일어난다.

6. 텅스텐으로 증착된 웨이퍼를 CMP로 연마시켜 상부 웨이퍼를 제거한다. 하부 산화물 절연체가 드러나면 텅스텐 플러그와 절연막으로 공간이 불리되는데, 이 부분이 BEOL 공정에서 배선이 연결될 구조이다.

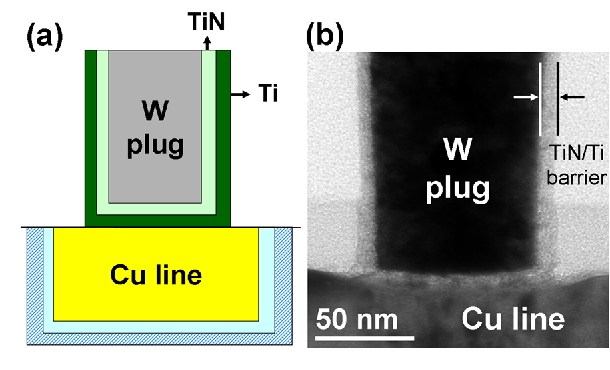

2) 텅스텐 플러그( W plug )

W plug(텅스텐 플러그)란 실리사이드 콘택트와 구리 배선 사이를 연결해주는 역할을 한다. 반도체 공정의 중간 단계이므로 MOL이라고도 불리며, 산화물 절연막 증착 후, 오믹 콘택트를 위해 만들어진 트렌치에 채워진 실리사이드 물질 위로 텅스텐을 채워 넣고 CMP 공정으로 절연막 표면이 들어날때까지 연마시킨다.

보다싶이 좁고 깊은 구덩이 형태에 채워넣는 방식이므로 CVD 방법을 통해 증착이 되며, 트랜치 안쪽이 다 채워지기 전에 개구부가 막히면 void가 생기고 이는 CMP 진행 후 관찰할 수 있다. 이를 Seam 현상이라고 하고, Seam 현상은 구리 배선 공정에서의 불량을 유발하므로, 온도와 Source 양, 압력 등의 공정 조건이 매우 중요하다.

W(tungsten)을 증착할 때 사용하는 source는 WF6로, 공정온도에서 불소와 해리 후 W는 성장하며 트랜치를 가득 채운다. 이때 남은 불소는 반응성이 굉장히 높기 때문에 Silicide 위에 바로 텅스텐을 증착 시 많은 문제가 발생한다. 따라서, 확산 방지막을 위에 덮는 과정이 필요하다.

확산 방지막 없이 텅스텐을 바로 증착하면 발생하는 문제

1. 볼케이노(Volcano) 불량

: 바닥면의 실리콘과 불소가 반응하여 용암이 폭발하는 것처럼 휘발성 반응물이 발생하는 것

2. 박리(Delamination)

: 측벽의 산화물 절연체와 불소가 반응할 때 산화물이 에치되는 것. 산화물 절연체가 제가되어 얇은 띠 모양의 공간이 발생하는 문제가 발생한다.

확산 방지막(Diffusion Barrier Layer)로는 TiN(티타늄 질화물)을 주로 사용한다.

적당한 두께의 TiN은 확산을 방지하고, 절연체 및 실리콘과의 반응을 억제하지만 두께가 지나치게 두꺼워지면 TiN 물질 자체의 저항이 금속보다 크기 때문에 최대한 얇게 깔아야한다. 또한 TiN에서 N의 농도가 높아지면, 확산 방지의 성능이 좋아지지만 저항이 커지기때문에 적당한 화학량비가 중요하다.

TiN은 CVD 방법으로 증착하는데, 바닥면과 트렌치의 측벽 모두 균일한 두께여야 하고, W을 후에 증착할때 개구부가 막혀있으면 안되기 때문이다. 따라서 최근에는 Ti 소스가 되는 물질과 Remote 플라즈마로 생성된 질소의 라디칼을 번갈아 가며 ALD 와 흡사한 증착 방식으로 증착하게 된다.

이렇게 TiN 막 위에 텅스텐이 성장하는데, TiN에서는 W의 nucleation이 일어나고, 공정이 계속되며 grain이 성장하면서 좁고 깊은 트렌치를 채워 나가게 된다. 이후 CMP 공정을 이용하여 산화물 절연막까지 평탄화 공정을 진행해 위쪽에 증착된 텅스텐을 제거해 W-plug와 산화물 절연막을 분리시킨다.

'반도체 공부 > 반도체 공정' 카테고리의 다른 글

| 반도체 공정 [21] 금속 배선 공정 (3) Cu 전해 도금 (Electroplating): 다마신(Damascene) 공정 (0) | 2025.02.17 |

|---|---|

| 반도체 공정 [20] 금속 배선 공정 (2) 알루미늄 배선과 구리 배선 (0) | 2025.02.17 |

| 반도체 공정 [18] 박막공정 (4) ALD(Atomic Layer Deposition) (0) | 2025.02.14 |

| 반도체 공정 [17] 박막공정 (3) CVD(Chemical Vapor Deposition) (6) | 2025.02.14 |

| 반도체 공정 [16] 박막공정 (2) PVD(Physical Vapor Deposition): Evaporation, Sputtering (2) | 2025.02.13 |