반도체 소자 [10] MOSFET (6) Channel(채널)과 증가형 / 공핍형

반도체 소자 [9] MOSFET (5) MOSFET에서의 I-V 특성 (Pinch-Off/ Saturation)반도체 소자 [8] MOSFET (4) MOSFET에서 상태 별 캐리어의 움직임과 I-V 특성 (Cut-Off/ Linear)반도체 소자 [7] MOSFET (3) MOSFET의 정의와 동작 원

mayunchem.tistory.com

반도체 가격은 동일한 조건일 경우 매년 약 30% 씩 떨어진다. 이를 보상하기 위해서는, 반도체 칩의 한정된 크기 내에서 트랜지스터(TR)의 개수를 늘려야 한다. 하지만, 이것도 뾰족한 방도가 없기 때문에 결국 Scaling Down 방식으로 TR의 크기를 물리적으로 줄여야 한다. 이 과정에서 가장 중요한 기능을 하는 'Channel'의 길이도 함께 짧아져야한다. 이번에는 TR이 평탄 타입일 경우, 이로 인해 발생하는 Short Channel Effect의 문제점과 해결방법에 대해 알아보아야 한다.

1. Scale-Down

반도체에서 가장 유명한 법칙은 인텔의 고든 무어가 발표한 '무어의 법칙'이다. 이것은 반도체 집적회로의 성능이 24개월마다 2배씩 증가한다는 법칙이다.

반도체는 위의 법칙처럼 점점 더 높은 집적화를 이루기 위해 개별소자의 크기가 점점 더 작아지고 있다. MOSFET 역시 미세화가 진행되면서, 저전력, 고속 동작을 달성하게 되었다.

MOSFET의 미세화에 있어서 소자 축소를 합리적으로 달성할 수 있는 방법이 제시되었다. IBM의 드나드는 게이트 길이만 감소시키는 것이 아니라 게이트 길이 감소에 따라 다른 항목들도 축소시켜 트랜지스터 내부의 전기장을 동일하게 유지하자는 등전기장 스케일링(Constant Field Scaling) 이론을 제시하였다.

이에 맞춰 MOSFET 소자의 미세화가 진행되었으나, 채널 길이가 짧아질수록 이를 만족할 수 없는 여러 효과들이 발생하였고 이를 통칭하여 '단채널 효과(Short Channel Effect)'라 한다.

'단채널 효과(Short Channel Effect)'는 좁은 범위에서도 넓은 범위로도 사용된다.

좁은 범위의 단채널 효과는 게이트 길이(채널의 길이)가 짧아짐에 따라 문턱 전압이 낮아지는 현상을 의미한다. 채널 길이가 짧아지면, 이 외에도 드레인 전압에 의한 장벽 저하(Drained Induced Barrier Lowering, DIBL), 펀치 -스루(Punch-Through), 캐리어의 속도 포화 현상(Velocity Saturation), 열 캐리어 효과(Hot Carrier Effect)등의 현상들이 발생한다.

2. Vt roll-off

'좁은 채널의 단채널 효과'는 채널 길이가 짧아짐에 따라 문턱 전압이 낮아지는 현상(Vt roll-off)을 의미한다. Vt는 문턱 전압으로, 트랜지스터가 켜지기 시작하는 최소 전압을 의미한다. MOSFET에서 주로 나타나는 단채널 효과 중 하나이다.

단채널 효과란 반도체 소자가 작아짐에 따라 채널의 길이가 짧아져서 전자층과 공핍층의 겹침 현상이 발생하여 전류가 새는 Leak Current가 발생하는 등의 문제점이 발생하는 것이다.

Vt Roll Off가 발생하는 이유는 무엇일까?

MOSFET의 임계전압인 Vt는 게이트 전압이 소스와 드레인 사이의 전도 채널을 형성하는 데 필요한 최소 전압이다. 이 값은 채널 길이와 여러 전기적 특성에 따라 달라지는데, 채널길이가 짧아질 수록 Vt는 낮아진다. 그 이유는 여러가지가 있는데, DIBL, 전위 분포 변화, 소스-드레인 간 전계 집중 등이 있다.

MOSFET에서 채널의 길이가 짧아지면 소스와 드레인의 전기장이 점점 가까워지며 게이트가 통제할 수 없는 영역이 늘어난다. 이 영역에서는 소스/드레인 자체가 일부 전위를 공급하는 역할을 하며, 게이트 전압 없이도 전도가 쉽게 이뤄진다. 원래 MOSFET은 게이트 전압이 충분히 높아야 채널이 형성되지만, 전하 공유 효과로 인해 게이트가 제어하는 채널 전하량이 감소한다. 결과적으로 낮은 게이트 전압에서도 채널이 형성되기 때문에 Vt가 감소하는 효과가 나타난다.

소자의 문턱 전압이 낮아지면, 오프 상태에서도 전류가 흐를 가능성이 있어 누설 전류가 증가하고, 전력 소비가 증가하기 때문에 전력 효율이 나빠져 소자의 성능이나 신뢰성이 저하될 수 있다. 이때 발생하는 누설 전류를 서브스레숄드 누설전류(Subthreshold Leakage)라고 한다.

이러한 Vt Roll-Off를 방지하기 위해 1. 채널 길이 증가, 2. High-K 유전체 및 금속 게이트 사용, 3. 다중 게이트 구조, 4. 소스-드레인 공학 등을 사용한다.

3. DIBL(Drain Induced Barrier Lowering, 드레인 전압에 의한 장벽 저하)

드레인 전압에 의한 장벽 저하 효과는 채널 영역에서 형성되는 내부 전위 장벽의 높이가 변하여 발생한다. 즉, Drain에 전압을 가하면 Drain 전압에 의해 공핍층이 생기고, 전류가 흐르는 길인 Source와 Drain 사이에 carrier가 넘어갈 Barrier가 낮아져 동작 전압이 낮아져 누설 전류(Leak Current)가 발생하는 것이다.

매커니즘을 정리해보자

1. Long Channel인 경우 Gate에 전압을 인가한 후 Drain에 인가하면 [1]번과 같은 Energy Barrier가 형성된다

= 전자가 Barrier의 높이만큼 뛰어넘어 Channel을 타고 Drain쪽으로 가는 상황이다.

2. Channel이 짧아지면 [3]과 같은 밴드 다이어그램이 형성된다. Drain에 전압을 인가하며 Barrier가 낮아져 Channel 층의 Barrier도 함께 낮아져 발생하는 현상이다.

이렇게되면 전자가 느끼는 에너지 장벽이 낮아져 누설전류가 생기는 것이다. 즉, Drain 전압으로 인해 Channel이 영향을 받으므로 MOSFET의 특성이 나빠지는 것이다.

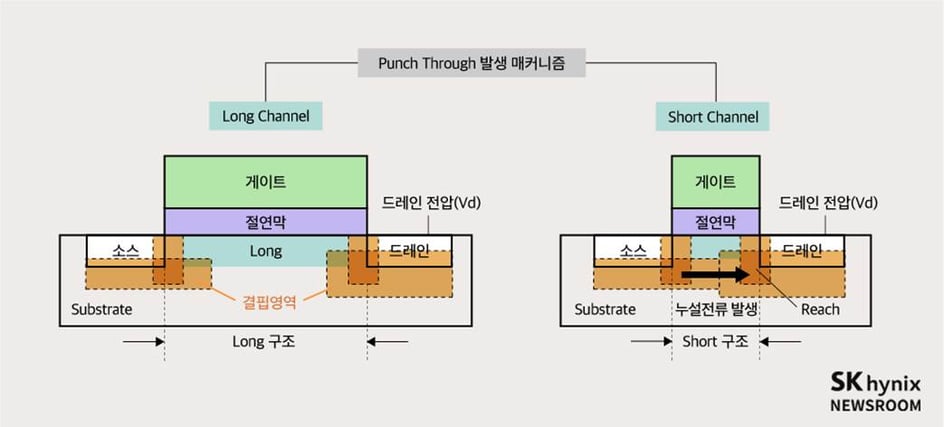

4. Punch-Through

소스와 드레인 단자에 동작 전압이 인가되면 각 정션에 Depletion Region이 생성된다. 이때, 드레인의 인가 전압이 높으므로 Source보다 상대적으로 Drain쪽이 큰 Depletion Region을 가진다. 이러한 상황에서 게이트의 길이가 줄어들면(= 소스와 드레인 사이의 물리적 거리가 충분하지 않으면), Drain 쪽에 형성된 Depletion Region이 Source 쪽의 Depletion Region과 겹치는 현상이 발생한다. 즉, 소스에서 드레인 쪽으로 결핍 영역을 통해 전류가 흐르게되고 Js에서는 순방향 전류(다수 캐리어 전자)가 JD에서는 역방향 전류(소수 캐리어 전자)가 흐른다. 이 두 전류는 모두 드레인 단자의 양전압으로 머리를 향하고, 이러한 전류는 게이트 전압이 통제할 수 없다. 따라서, 트렌지스터의 On/Off에 기여하지 못하는 누설 전류가 된다.

Long Channel에서 정상적인 드레인 전류는 게이트 전압에 의해 통제되고, 드레인 전압을 과도하게 증가시켜도 전류가 포화되므로 일정 한도내에서는 더이상 증가하지 않는다. 하지만, Short Channel에서는 하부 결핍 영역이 연결된 경우, 드레인 전압에 비례하여 누설 전류가 무한정 이차함수 꼴로 증가하므로, 계속 드레인 전류를 증가하면 트렌지스터가 파괴되거나 동작 불량 상태가 된다.

해결방안

Jd의 결핍 영역이 형성될 공간을 막아야하므로, 내부 구조를 일부 변경해야한다.

1) 소스와 드레인 단자 하부에 절연층인 SOI를 형성해 소스나 드레인 하부에 결핍 영역이 형성되지 못하게 강제로 원천봉쇄한다.

2) 구조는 기존의 형태를 유지하되, 소스와 드레인 단자의 하부에 P-type 기판 단자의 농도보다 더 높은 농도의 불순물로 이온 주입을 해두면 결핍 영역의 형성을 어느정도 방지할 수 있다. 이를 Halo Doping이라고 한다.

NMOS의 경우 p+로 도핑을 하고, pMOSFET의 경우 n+로 도핑하기 위해 불순물 도즈를 가장 높게 책정해 이온주입을 한다.

Halo Doping을 하였을 때, 어느정도 채널길이가 감소할 때까지 오히려 문턱전압이 증가하는 반 단채널 효과(Reverse Short Channel Effect, RSCE) 현상도 일어난다. 이는 불순물 활성화 과정에서 진행하는 고온 열처리가 원인이다.

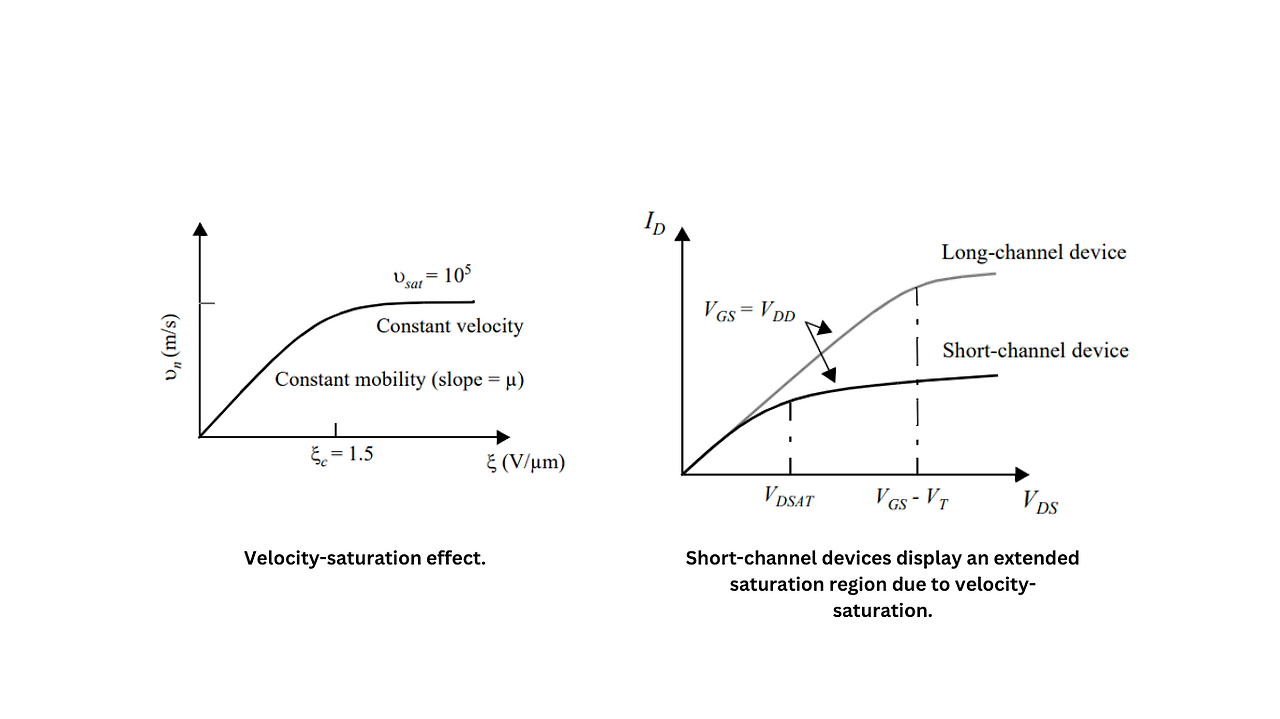

5. 속도 포화 현상(Velocity saturation)

속도 포화 현상이란 캐리어가 매우 큰 속도로 발생되었을 때 발생하는 현상으로, On 상태의 드레인 전류를 현저히 낮추는 문제를 일으킨다. 캐리어의 속도는 일정 전기장 하에서는 전기장에 비례하다가 강한 전기장이 인가되면 특정 속도에서 포화된다. 이는 캐리어의 속도가 커질 수록 캐리어가 인접한 격자들과 충돌할 가능성이 높아지기 때문이다. 캐리어에 인가되는 에너지가 증가하여도, 에너지가 속도 증가에 기여하는 것이 아닌 실리콘 격자 내로 전달되어 격자를 때린다.

이러한 속도 포화 현상은 단채널 트랜지스터에서 더 크게 나타난다. 일정 전압에서 전기장은 거리에 반비례하기 때문에 채널 길이가 낮을 수록 채널에 인가되는 전기장이 훨씬 크게 작용한다. 이에 단채널 소자에서는 핀치 오프가 일어나기 전보다 더 낮은 드레인 전압에서 캐리어의 속도 포화 현상이 발생하며, 이에 따라 전류의 포화 역시 장채널보다 더 낮은 전압에서 일어난다.

장채널 소자에서는 포화상태의 드레인전류가 게이트 전압의 제곱에 비례하나, 단채널 소자에서는 게이트 전압과 선형적으로 증가하게 된다.

6. 열 캐리어 효과(Hot Carrier Effect)

MOSFET의 채널 길이가 짧아지면 채널 방향의 전기장이 증가한다. 이때 채널 내의 전기장은 등간격으로 분포하는 것이 아닌 특정 영역에서 최대치를 가진다. 따라서 이러한 강한 전기장 내에서 캐리어는 소스에서 드레인으로 움직이면서 높은 에너지를 받게된다. 이렇게 높은 에너지를 가진 전자를 '열 캐리어(Hot Carrier)'라고 한다.

nMOS를 예를 들어 설명해보자.

캐리어인 전자는 채널을 따라 이동할 때 일자로 직진하는 것이 아닌, 산화막 경계면에 충돌을 거듭하며 드레인으로 이동한다. 이들 산화막은 형성 시 실리콘과의 계면에서 불포화 결합(Dangling Bond)이 형성되어있는데 이들은 전자의 이동을 방해하는 Trap으로 작용한다. 불포화 결합을 제거하기 위해 보통은 수소 환경의 열처리를 통해 피복 시킨다. 이때 높은 에너지를 가진 열전자는 충돌을 통해 수소 결합을 끊어 다시 불포화 결합 상태를 복원시킨다.

불포화 결합 상태에 의해 계면에 전자가 포획되거나 전기력에 의해 전자의 움직임을 방해받아 이동도가 감소한다. 이동도의 감소는 전달 전도도(Transconductance)의 감소로 이어지고 이는 On 상태의 전류 감소와 고주파 특성의 저하를 불러온다. 또한, 게이트 산화막에 전자가 포획되면 산화막 내의 추가적인 전하를 형성하기 때문에, 게이트의 전압이 채널에 전달되는 것을 방해한다. 따라서, 채널을 반전시키는데 필요한 Vth(문턱 전압)이 증가하고 소자의 신뢰성을 감소시킨다.

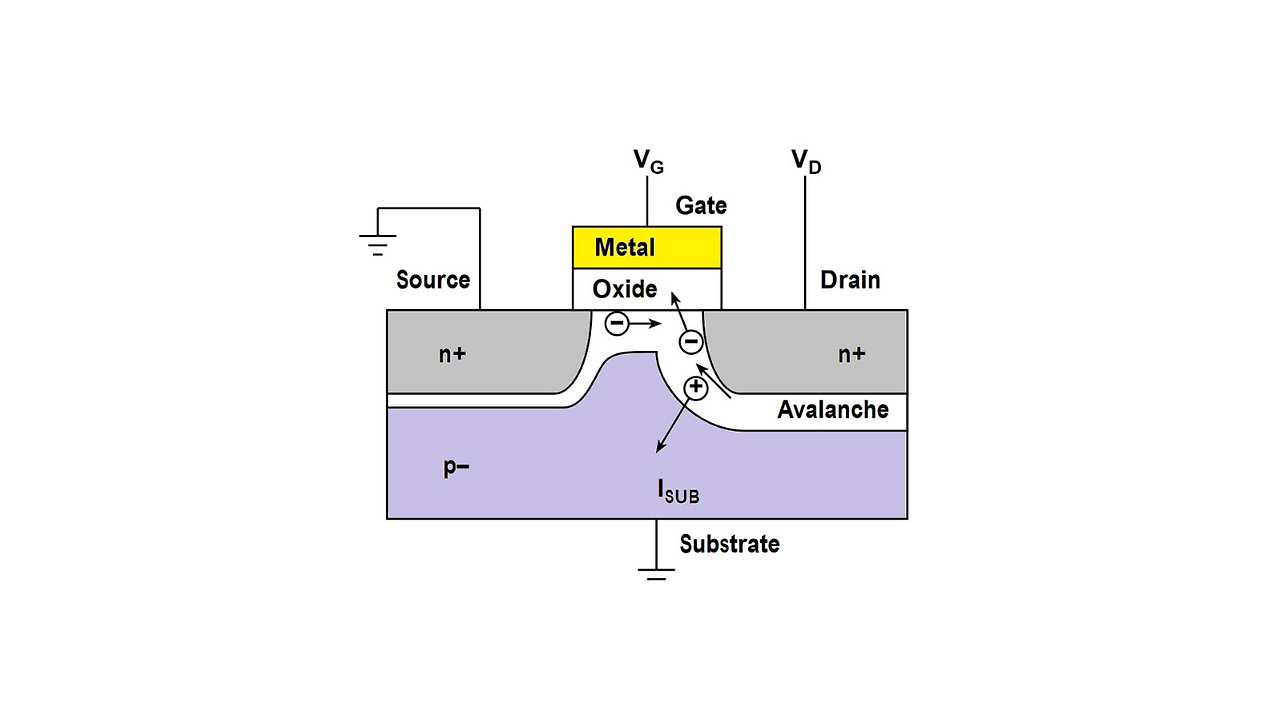

Hot Carrier는 이외에도 '충돌 이온화(Impact Ionization)'을 일으킨다.

Hot Carrier가 실리콘 격자와 충돌하면 전자-정공쌍이 생성되고 이들은 다시 에너지를 받아 실리콘 격자와 충돌하여 또다른 전자-정공쌍을 생성시킨다. 이러한 cycle이 반복되면서 전자와 정공이 대량생산되고 그 중 전자는 양전압이 인가된 드레인으로 정공은 기판으로 빠져나가면서 기판 전류(I_sub)를 형성한다. 형성된 기판 전류는 저항으로 인해 기판 내 전위차를 발생시켜 결과적으로 기판의 전위가 0V인 소스보다 높아진다. 이에 소스- 기판 -드레인이 BJT 동작을 하게 되어 기판을 통해 드레인으로 이동하는 전자가 증가하는 Snap-Back 현상을 일으킨다.

또한, nMOS와 pMOS가 맞물린 CMOS 구조에서는, 기판의 BJT가 서로 맞물려 레치업(Latch Up) 현상 등의 원치 않는 불량을 일으키기도 한다. 이와 같은 현상을 통틀어 Hot Carrier Effect이라고 한다.

Snap-Back 현상

: 드레인 전류가 정상적으로 흐르다가 갑자기 증가하는 현상

Latch-up(레치업)

:CMOS에서 내부 접합부 일부가 도통되어 순간적인 과전류가 흘러 소자 및 회로를 파괴시키는 현상

위와 같은 Hot Carrier Effect는 보통 nMOS와 전자에 의해서만 발생하는 것으로, Hot Electron Effect라고 부르기도 한다.

해결방안

열 캐리어 효과를 줄이는 가장 대표적인 방법은 저농도 도핑 드레인(Lightly Doped Drain, LDD) 기법이다. 이에 대한 내용은 다음 링크를 참고하도록 하자. 추가로 다음 시간에 다루도록 하겠다.

https://news.skhynix.co.kr/post/spacer

[반도체 특강] 스페이서(Spacer), 철갑을 두른 게이트

반도체 소자 구조에서 스페이서(Spacer)란, 게이트 단자의 사면을 Side Wall 형태로 둘러싼 절연막입니다. 스페이서는 게이트 단자를 보호하는 역할도 하지만, 초창기의 목적은 하부에 도핑된 LDD 영

news.skhynix.co.kr

7. 기생 저항과 기생 정전 용량

미세화가 진행될수록 MOSFET 소자의 기생 저항(Parasitic Resistance)와 기생 정전 용량(Parastic Capacitance) 문제가 대두되고 있다. 이들은 신호의 전달을 지연하는데, 도선의 끝에 전달되는 신호는 기생 저항과 기생 정전 용량의 곱에 따라 커지며 이를 RC relay라고 한다. RC relay는 소자의 성능을 열화시키기 떄문에 이를 최소화해야한다.

기생 저항은 소자에 존재하는 여러 저항을 나타내며, 이 중 채널 저항과 외부 드레인 저항은 소자의 문턱 전압과 전류의 크기, 신뢰성에 영향을 주기 때문에 줄이기 쉽지 않다. 오히려 미세화가 진행되며 영향을 받는 부분은 소스/드레인 저항과 소자-배선 간의 접촉 저항이다.

소스/드레인 저항은 DIBL, Punch-Through 등의 단채널 효과를 줄이기 위해 Shallow Junction을 사용하며 증가하는 경향을 보인다. 또한 MOSFET의 크기가 작아지면서 배선에서부터 소스/ 드레인에 연결하는 단면적이 감소하며 접촉저항 역시 증가한다. 이들을 줄이는 방법으로 소스/ 드레인 영역의 '재성장(Regrowth)'하는 방법이 대두되었다.

이는, 소스/드레인을 얕게 파낸 후 높은 도핑 농도를 가지는 소스/드레인이 실리콘 표면 위로 올라가는 형태를 만드는 것으로, 얕은 접합을 유지하고 고농도 도핑으로 소스/드레인 저항을 낮추고, 배선간의 간격을 줄여 접촉 저항을 줄일 수 있다.

기생 정전용량은 채널층 형성을 위한 게이트-산화막-반도체의 정전 용량을 제외한 나머지 정전 용량을 의미한다. MOSFET 소자에서는 주로 게이트와 소스/드레인 간의 정전 용량이 이를 차지 하기 때문에, 이를 줄이기 위해 스페이서(Spacer)을 저 유전물질(low-k)로 형성하는 기법을 사용한다.

'반도체 공부 > 반도체 소자' 카테고리의 다른 글

| 반도체 소자 [10] MOSFET (6) Channel(채널)과 증가형 / 공핍형 (2) | 2025.03.01 |

|---|---|

| 반도체 소자 [9] MOSFET (5) MOSFET에서의 I-V 특성 (Pinch-Off/ Saturation) (0) | 2025.03.01 |

| 반도체 소자 [8] MOSFET (4) MOSFET에서 상태 별 캐리어의 움직임과 I-V 특성 (Cut-Off/ Linear) (0) | 2025.02.28 |

| 반도체 소자 [7] MOSFET (3) MOSFET의 정의와 동작 원리 (2) | 2025.02.28 |

| 반도체 소자 [6] MOSFET (2) 문턱 전압 (0) | 2025.02.28 |