박막공학 [21] CVD 공정 (4) ALD 공정, High-K/ Low-K

박막공학 [20] CVD 공정 (3) CVD SiO2의 막 특성, DEP & ETCH/ TEOS-O3 기술, Metal CVD박막공학 [19] CVD 공정 (2) CVD 공정의 kinetic modeling과 epitaxy/ Polycide 공정박막공학 [18] CVD 공정 (1) APCVD, LPCVD, PECVD2025.08.06 - [학

mayunchem.tistory.com

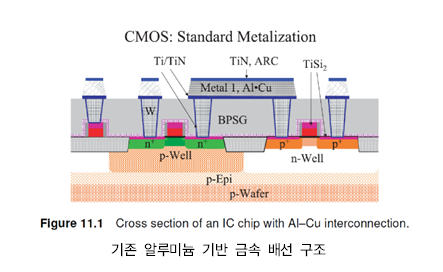

CMOS에서 가장 기본적인 metallization구조를 살펴보자.

| Ti/TiN 층 | - Ti/ TiN: Al과 산화막의 접착력 향상 - TiN : Al이 실리콘으로 확산되는 것을 막음 , ARC (Anti-Reflection Coating) 역할 |

| Al–Cu 배선층 | 전자 이동 내구성(Electromigration)에 강함 PVD로 증착 |

| TiSi₂ 층 | - Poly-Si와 금속 간의 접촉 저항을 줄이기 위해 형성 |

| BPSG | 층간 절연막 (ILD) → 평탄화 목적 CVD + Flow + Annealing으로 증착 |

| 기판 하부 | n-Well / p-Well / Epi / Substrate 구조로 일반적인 CMOS 구조 |

Interconnection

: MOS 소자와 주변 회로를 연결하여, 반도체 제품의 회로를 연결하는 도체 재료의 구성을 의미한다.

Interconnection의 구성은 다음과 같다.

1. 전류와 전압을 전달하는 배선 라인 ( Al – Cu, W, Cu, N+/P+ Poly-Si)

2. Source/Drain 접합의 Sheet Resistance를 낮추기 위한 Silicide ( Si + Co, Ni, Ti )

3. 접합의 Diffusion을 막아주는 Diffusion Barrier

4. 반사를 막아주는 TiN ARC

5. 접합력을 높여주는 adhension (Ti/TiN)

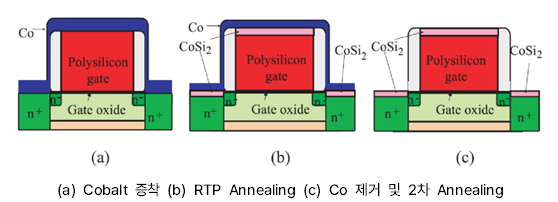

1. Salicide 공정

Salicide (Self-Aligned Silicide) 공정

: 게이트 및 소스/드레인 영역에 저항이 낮은 금속 실리사이드(silicide)를 자동 정렬 방식으로 형성하는 공정

전극 재료가 Poly-Si나 Si이면 전기 저항이 크고 속도가 느리기 때문에 여기에 저항이 작은 금속 재료(금속 실리사이드)를 입혀 성능을 개선하는 것이다.

그림으로 나타내면 다음과 같다.

2. Junction Spiking

Junction Spiking

: CMOS 소자에서 알루미늄(Al) 금속 배선이 소스/드레인 영역의 실리콘(n+ or p+)과 직접 맞닿는 경우, 특정 조건에서 Al이 실리콘 속으로 침투하는 것

고온에서 열이 가해지면 Al이 액체처럼 Si 속으로 스미는데 이때 PN 접합을 뚫으면 소자 불량이 발생한다. 따라서, 고온 열처리를 하거나 접촉 면적이 좁을 때, 혹은 순수한 Al을 사용시 잘 발생한다.

3. Electro-migration

Electro-migration

: 전류가 흐를 때, 금속 배선 안의 금속 원자들이 전자 흐름 방향으로 조금씩 이동하면서 배선이 손상되는 현상

금속이 움직일 때 어떤 곳은 금속이 부족해서 끊기고, 어떤 곳은 금속이 몰려서 돌출되는데 이러한 현상은 전기적 단선, 단락을 일으킬 수 있다. 이러한 개선을 위해 Al대신 Al-Cu 합금을 사용하고 있다.

4. 저 저항 Metal 배선의 필요성

RC Delay graph를 보자. Delay = R C로 배선폭이 줄어들 수록 R, C가 증가하기 때문에 Delay가 증가한다. 따라서 R이 작은 저 저항 metal 배선의 필요성이 커지고 있다.

관련 수식을 예제로 살펴보자.

metal line 폭 = 10nm, pitch = 20nm, 배선 길이 = 1cm일 때 총 배선 길이는 얼마일까?

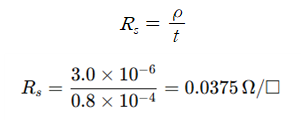

이때 Al의 금속 두께는 0.8 μm이고, Al의 비저항 ρ = 3.0 μΩ·cm

해설)

1) 총 금속 배선 길이 (1 cm 칩에 들어갈 라인의 수)

2) Sheet Resistance

3) 전체 저항 R 계산

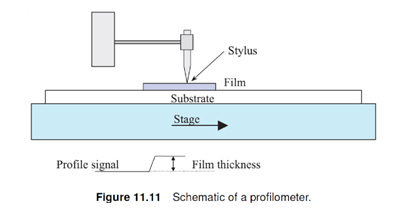

5. Metal Film의 두께 측정 방법

1) Profilemeter의 사용

2. Acoustic thin film mesurement (음향 반사법)

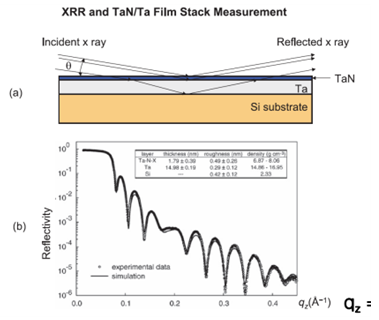

3) X-ray Reflectometry (XRR) – X선 반사법

X ray의 입사각이 매우 작으면 표면에서 반사되는 것을 이용한 방식으로, 상단 표면 및 계면에서 반사되어 간섭 패턴이 발생한 것을 분석하여 막의 두께, 밀도, 거칠기를 측정한다.

'학교 수업 > 박막공학' 카테고리의 다른 글

| 박막공학 [24] Photolithography(2) (3) | 2025.08.27 |

|---|---|

| 박막공학 [23] Photolithography (1) (7) | 2025.08.26 |

| 박막공학 [21] CVD 공정 (4) ALD 공정, High-K/ Low-K (3) | 2025.08.16 |

| 박막공학 [20] CVD 공정 (3) CVD SiO2의 막 특성, DEP & ETCH/ TEOS-O3 기술, Metal CVD (1) | 2025.08.16 |

| 박막공학 [19] CVD 공정 (2) CVD 공정의 kinetic modeling과 epitaxy/ Polycide 공정 (2) | 2025.08.16 |