박막공학 [20] CVD 공정 (3) CVD SiO2의 막 특성, DEP & ETCH/ TEOS-O3 기술, Metal CVD

박막공학 [19] CVD 공정 (2) CVD 공정의 kinetic modeling과 epitaxy/ Polycide 공정박막공학 [18] CVD 공정 (1) APCVD, LPCVD, PECVD2025.08.06 - [학교 수업/박막공학] - 박막공학 [17] Deposition(증착) (2) PVD 공정: Evaporation 공

mayunchem.tistory.com

1. ALD 공정

ALD 공정

: 화학적 흡착 및 탈착을 이용하여 원자를 한층씩 정밀하게 증착하는 반응.

ALD 공정의 특징은 다음과 같다.

1) S/C가 매우 좋다

ex. A/R이 40 이상인 DRAM의 capacitor dielectric의 증착에 사용

2) 증착 속도가 느리다

3) 두께 정밀 제어가 가능하다

4) 사이클 수가 늘어날수록 두께는 선형적으로 증가

2. High-k dielectric Materials

유전율 k가 커질 수록, 더 얇은 유전체로 더 높은 정전 용량을 확보할 수 있다. 이때 Eg와 ΔE도 높아야 누설 전류 방지 가능하다.

그래프를 보면, 오른쪽으로 갈 수록 유전율이 크고 위로 갈 수록 Eg(band gap)이 크다. 따라서, 적절한 high-K물질이 필요하다.

이러한 High-K 대표 적용 분야는 MOS 소자의 Gate 유전체, DRAM의 Capacitor 등이 있다.

3. Low-K + Cu 공정

2000년대 이전, 금속 배선으로 Al을 사용하였고 절연층은 SiO2 (k = 3.9)를 사용하였다. 하지만, 공정 미세화로 인한 배선 간격이 좁아지며 Delay의 극복을 위한 속도 향상이 필요해졌고, Al → Cu로 대체하는 다마스커스 공정과 SiO2 → Low –k 재료로 바꾸었다.

Damascene 공정

: Cu는 플라즈마 식각이 어렵기 때문에 구멍(trench)를 먼저 만들고 Cu를 채운 후 CMP로 위를 평탄화 하는 공정

cf. Delay = R*C이므로 delay를 줄이기 위해선 저항(R)을 줄이거나 C를 줄여야 한다.

유전율을 줄이는 방법은 여러가지가 있는데, 그 중 몇가지만 소개하자면 다음과 같다.

불소(F)를 도입하는 방법을 추가로 살펴보면, F가 O를 대체하여 도핑하는 방식으로, Si-F 결합으로 인해 전자 분극이 줄어들어 유전율이 낮아지며, 습기 흡수에 취약하다는 단점이 존재한다.

불소가 아니라 CH3를 O대신 도핑하는 방법도 존재한다. C-doped Organosilicate Glass (SiOC, OSG)라고 하며, Si-CH3 구조를 형성하는 방식이다. 전기적으로 안정하며, 분극이 낮고 수분에 강하다.

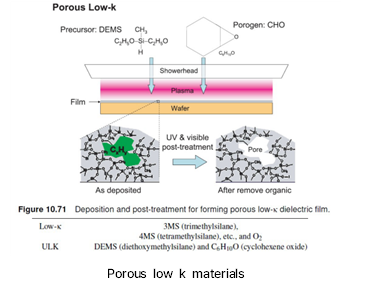

또한, 기공을 의도적으로 만들어내는 방법도 있다. 이를 Porous Low-k 방식이라고 하며, 공기의 유전율은 k= 1로 이론적으로 가장 낮기 때문에 유전체 내부에 공기를 포함시키면 전체 유전율이 낮아지는 효과를 얻어낼 수 있다. 이를 위해 재료 내부에 기공을 의도적으로 형성한다.

또한, Low-k 절연층 내에 존재하는 유기물을 열이나 플라즈마로 휘발시켜 내부에 빈 공간을 남겨 Air Gap을 형성하기도 한다.

'학교 수업 > 박막공학' 카테고리의 다른 글

| 박막공학 [23] Photolithography (1) (7) | 2025.08.26 |

|---|---|

| 박막공학 [22] Metallization (6) | 2025.08.26 |

| 박막공학 [20] CVD 공정 (3) CVD SiO2의 막 특성, DEP & ETCH/ TEOS-O3 기술, Metal CVD (1) | 2025.08.16 |

| 박막공학 [19] CVD 공정 (2) CVD 공정의 kinetic modeling과 epitaxy/ Polycide 공정 (2) | 2025.08.16 |

| 박막공학 [18] CVD 공정 (1) APCVD, LPCVD, PECVD (1) | 2025.08.16 |