반도체 특강 [4] 결핍영역 Depletion Layer

반도체 특강 [3] 20세기 최고의 발명품, 점 접촉 트랜지스터반도체가 비교적 다른 발명품보다 늦게 등장한 이유는 절연체, 반도체, 도체 틍성을 갖는 물체들을 서로 연이어 붙일 때 두 개의 물성

mayunchem.tistory.com

반도체가 실생활에 많이 사용되는 이유는 절연체 성질을 가지는 물질에 약간의 화학적 물질을 첨가하여 절연체를 도체에 가까운 성질로 변화시킬 수 있기 때문이다. 도체를 통제하는 수단은 도체 외부에서 인가하는 '플러스, 마이너스' 전압의 2단 논리이다. 하지만 이것들만으로는 원활하게 사용하기 어렵기 때문에, 이때 공핍층이 매우 중요한 매개 수단이 된다.

전압에 따라 변화하는 Gate 공핍층

트랜지스터는 외부 통제 수단으로 6단 논리(NPN, PNP의 각 단자 +/- 전압)을 적용하고, 내부 통제 수단으로는 공핍층이 2개 더 있다. 이렇게 총 8단의 논리를 이용하여 트랜지스터를 의도하는 목적과 다양한 측면에서 활용할 수 있다.

| 트랜지스터의 외부 통제 수단 | 6단 논리(NPN, PNP의 각 단자 +/- 전압) |

| 트랜지스터의 내부 통제 수단 | 공핍층이 2개 |

따라서 공핍층은 트랜지스터/ 다이오드를 동작하는데 중요한 매개수단이다.

일반적으로 트랜지스터의 공핍층은 제일 중요한 공핍층으로 P-N접합과 N-P 접합 사이에서 생성된 2개의 공핍층(Source 공핍층/ Drain 공핍층)이 존재한다. 그런데 'MOSFET 공핍층'은 'Gate/ 확산/ 순방향 Bias/ 역방향 Bias 공핍층' 총 4개로 세분할 수 있으며 이들의 상호작용을 통해 트랜지스터를 동작시키킨다.

Gate 공핍층

Gate 단자에 (+) 전압을 인가 (Source= Drain = 0 V)하면서 Substrate는 약간의 (-) 전위를 가진다. 그러면 P_substrate 단자 내 소수 캐리어인 전자들이 gate 단자의 (+) 전압에 의해 P_sub의 상단으로 이동한다. 전자가 있던 빈자리는 (+) 로 대전된 층이 남게 되고 전자가 결핍된 이 공핍층은 Gate 단자에서 멀어질 수록 농도가 약해지고 전자들은 P_sub의 상단 경계면에 밀집한다.

P_sub내 (+)로 대전된 정공층은 Gate 전압으로 인해 탄생하기 때문에 'Gate 공핍층' 이라고 부른다.

Substrate 공핍층이라고 해도 되지만, Sub 영역에는 트랜지스터 내부 동작 순서에 따라 '확산 공핍층→Gate 공핍층→바이어스 공핍층(순방향, 역방향) '순으로 여러 개의 공핍층들이 등장하므로 각 공핍층을 구분해서 부르는 것이 혼돈을 방지하는데 도움이 된다.

P_sub 내에 존재하는 정공들은 1) 전자가 빠져나가서 형성한 인위적인 정공들(= (+) 극성으로 대전된 원자집단인 공핍층)과 2) 초창기 P_type 불순물 반도체를 만들며 자연스레 생성된, 다수 캐리어라고 불리는 정공으로 구성된다.

P_sub 를 형성하는 불순물 농도는 Source/ Drain 단자에 비해 10만분의 1배로 약하게 형성된다. 이에 불순물 농도에 반비례하는 'Gate 공핍층'의 두께는 확산 공핍층에 비해 넓게 형성된다. 또한, Gate 단자 전압 변화에 따라 'Gate 공핍층'의 두께가 변하기도 하는데 이를 '공핍층 Modulation'이라고 한다.

확산 공핍층과 바이어스 공핍층(Bias)의 상관관계

반도체 특강 [4] 결핍영역 Depletion Layer

반도체 특강 [3] 20세기 최고의 발명품, 점 접촉 트랜지스터반도체가 비교적 다른 발명품보다 늦게 등장한 이유는 절연체, 반도체, 도체 틍성을 갖는 물체들을 서로 연이어 붙일 때 두 개의 물성

mayunchem.tistory.com

지난 시간에 다루었던 두개의 공핍층이 확산 공핍층이라고 할 수 있다.

'확산 공핍층'이란 외부에서 인가되는 전압없이, '화학 접합면에서의 확산 에너지에 의해 자연히 생성되는 층'이다. Source와 Drain 불순물 농도만 같으면, 두 공핍층은 서로 대칭이며 동일한 두께를 갖는다.

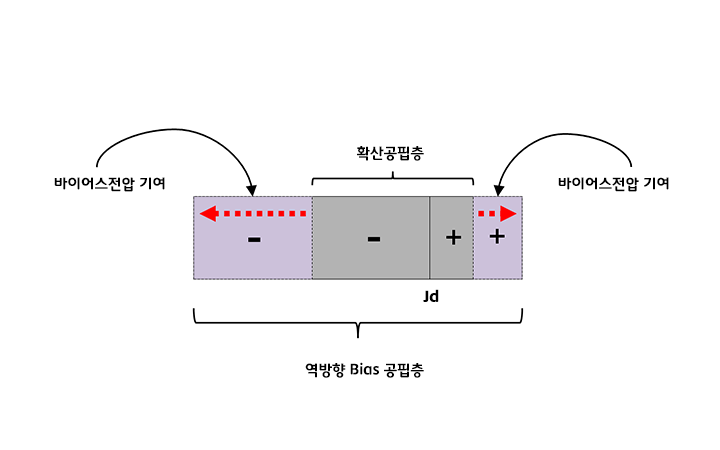

Gate 단자에 (+) 전압이 인가된 상태를 유지하면서, 트랜지스터가 정상적으로 Switching 하는 조건인 Source = 0V , Drain = + Vd를 가한다. 그러면 Drain 단자의 (+) 전압으로 인해 확산/공핍 층 모두 두께가 변하는데, 바이어스 전압으로 인해 공핍층의 두께가 바뀐 것이기 때문에 이를 '바이어스 공핍층'이라고 한다.

Source Junction(Js)에서 바이어스 공핍층은 원래 확산 방식으로 형성된 공핍층보다 공핍 영역이 좁아지고(순방향 바이어스 공핍층), Drain Junction 에서의 바이어스 공핍층은 공핍 영역으로 더욱 넓어진다(역방향 바이어스 공핍층).

순방향 Bias 공핍층

순방향/ 역방향 기준은 다수 캐리어가 정상 혹은 반대로 흐르느냐로 결정한다. 다수 캐리어가 Junction을 가로질러 정상으로 흐를때를 '순방향 바이어스 공핍층'이라고 하고, 반대방향으로 움직일 때 형성된 공핍층을 '역방향 바이어스 공핍층' 이라고 한다.

Source Junction(Js)을 가운데에 두고 전계 에너지와 확산 에너지가 평형 상태에 있는 확산 공핍층에 순방향 바이어스 전압을 걸면, 균형이 무너지며 전계에너지가 확산 에너지보다 증가한다. 그에 따라 Source 단자에 있는 다수 캐리어인 전자들이 Drain 단자의 (+) 전압을 향해 대거 이동한다. 그러면서 (+)로 대전된 Donor 이온의 많은 Hole을 매꾼다. 마찬가지로, Js의 P_sub side에 형성된 공핍층에도 P_sub의 다수 캐리어인 hole이 달려들어 확산 형식으로 형성된 공핍층의 두께를 절반 가까이 줄게한다. 이때 흐르는 다수 캐리어인 전자와 hole의 개수는, 순수 반도체 상태의 실리콘에서 빠져나오는 것에 비해 1억배~ 100억배 가까이 된다.

역방향 Bias 공핍층

반면, Drain 단자에 같은 전압을 인가할 때, Drain Junction(Jd) 양쪽에 형성된 공핍층에는 Js 양쪽 공핍층과 반대 현상이 발생한다. Drain 단자에 인가된 (+) 전압이 Drain 단자 내의 전자를 잡아당기고, P_sub 단자 내의 hole을 밀어내기에, 확산방식으로 형성된 공핍층 두께가 Jd를 기준으로 해서 양쪽으로 더욱 넓어진다.

Drain 공핍층의 두께가 형성되는 과정을 보자.

Jd Drain 단자에 1차로 형성된 확산 공핍층은 P_sub의 다수 캐리어인 hole이 Jd를 넘어와 형성한 공핍층(+Donor)이다. 2차로 넓어지는 역방향 공핍층은 Drain단자 자체 내의 다수 캐리어인 전자가 중성 상태의 N+ type 단자에서 빠지며 만든 공핍층(+Donor)이다. 공핍층 중에는 역방향 Drain 공핍층이 순방향 Source 공핍층보다 트랜지스터 동작에 더욱 큰 영향을 끼친다.

결국, 역방향 공핍층에서는 Jd를 넘는 다수 캐리어는 사라지고, 소수 캐리어(전자, hole)만 Drain Junction을 지난다. P type의 소수 캐리어 전자가 N+ type source 단자에서 넘어온 다수 캐리어인 전자와 합쳐, MOSFET을 흐르는 대전류가 되어 Switching 작용의 주인공이 된다.

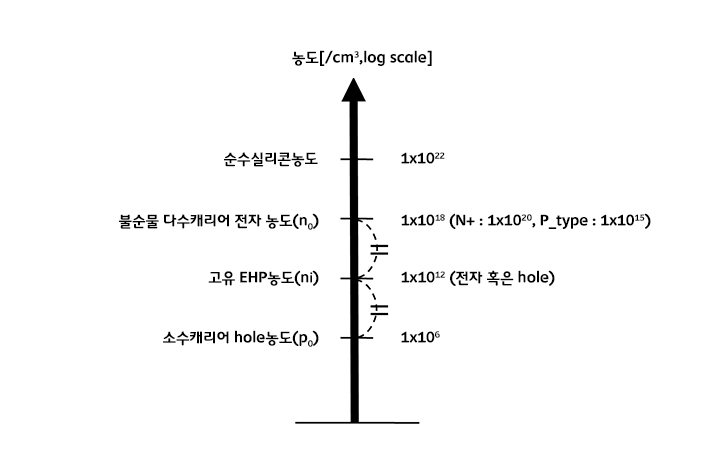

다수 캐리어와 소수 캐리어의 관계

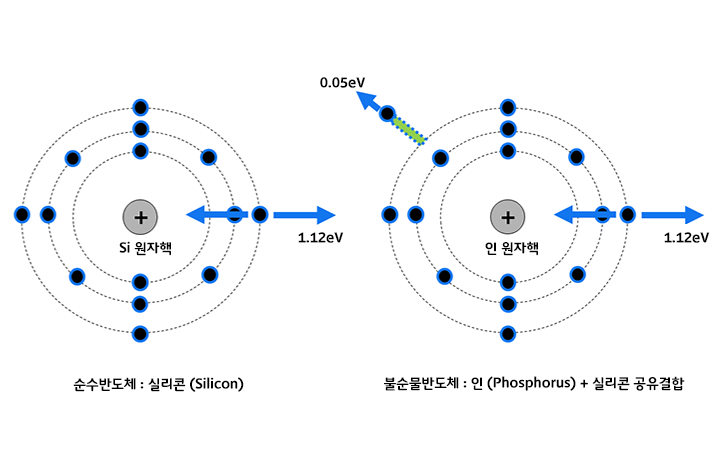

다수 캐리어의 원천이 불순물 원소(Doping을 하는 Dopant)인 반면, 소수 캐리어의 원천은 순수 실리콘 원소에서 발생하는 고유 캐리어인 전자나 정공이다. 예를 들어, 순수 Si는 순수 실리콘의 농도가 10^22/ cm^3일 경우 상온에서 전자 - 정공 Pair(EHP)로 10^10 ~ 10^12개 정도가 발생한다. 실리콘 원자가 전자를 다시 포획해 EHP를 소멸시키기도 한다. 여기에 15족 원소를 Si 원소의 1/100 정도로 도핑을 시키면 N type의 전자가 10^20정도 탈출하려 한다.

그 후 외부에서 알맞은 전위를 가하면, N type 불순물 원자 내 전자들은 다수 캐리어가 되어 움직인다. 이때 고유 반도체에서 생성된 EHP 중 전자는 다수 캐리어인 전자들의 숫자에 묻힌다. 정공은 다수 캐리어(전자)에 의해 소멸해 상쇄된 숫자를 의미하고, 살아남은 정공들이 다수 캐리어를 피해 소수 캐리어로 활동한다. 따라서, 소수 캐리어의 숫자는 순수 EHP 개수를 넘지 못하고 불순물(Dopant) 다수 캐리어 농도에 반비례한다.

공핍층을 만드는 에너지

불순물 반도체의 장점은 트랜지스터를 동작하는 에너지의 소모가 적다는 것이다.

같은 전자라도 (불순물 반도체로부터 잉여 전자를 떼어내는 에너지) = (순수 반도체로부터 최외각 전자를 탈출시키는 에너지) * 1 /20 정도이다. 매우 작은 에너지로도 불순물 중성 원자를 이온화시킬 수 있기 때문에, 반도체 제조 공정을 꿈의 연금술이라고 할 수 있다. 확산 공핍층과 바이어스 공핍층을 쉽게 만들고 이를 기반으로 Drain 단자에 가하는 전압을 낮춰 더 낮은 전력을 소모하는 친환경 반도체도 가능해진다.

참고자료

https://news.skhynix.co.kr/the-deprived-the-crystal-of-alchemy/

[반도체 특강] 공핍층, 연금술의 결정체 | SK hynix Newsroom

반도체가 실생활에 많이 활용되는 이유는 ‘쉬운 연금술’ 때문입니다

news.skhynix.co.kr

'SK 하이닉스 뉴스룸' 카테고리의 다른 글

| 반도체 특강 [4] 결핍영역 Depletion Layer (0) | 2025.03.10 |

|---|---|

| 반도체 특강 [3] 20세기 최고의 발명품, 점 접촉 트랜지스터 (0) | 2025.03.07 |

| 반도체 특강 [2] 자유 전자 (1) | 2025.03.06 |

| 반도체 특강 [1] 전자의 발견 (0) | 2025.03.06 |